### Intel Architecture Software Developer's Manual

# Volume 2: Instruction Set Reference

**NOTE**: The *Intel Architecture Software Developer's Manual* consists of three volumes: *Basic Architecture*, Order Number 243190; *Instruction Set Reference*, Order Number 243191; and the *System Programming Guide*, Order Number 243192.

Please refer to all three volumes when evaluating your design needs.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel's Intel Architecture processors (e.g., Pentium® processor, Pentium processor with MMX™ technology, and Pentium Pro processor) may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Such errata are not covered by Intel's warranty. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect IL 60056-7641

or call 1-800-879-4683 or visit Intel's website at http:\\www.intel.com

Copyright © Intel Corporation 1996, 1997.

\* Third-party brands and names are the property of their respective owners.

**PAGE**

| CHAPT                           | ER 1                                                                                                |      |

|---------------------------------|-----------------------------------------------------------------------------------------------------|------|

| ABOUT                           | THIS MANUAL                                                                                         |      |

| 1.1.                            | OVERVIEW OF THE INTEL ARCHITECTURE SOFTWARE DEVELOPER'S MANUAL, VOLUME 2: INSTRUCTION SET REFERENCE | 1-1  |

| 1.2.                            | OVERVIEW OF THE INTEL ARCHITECTURE SOFTWARE                                                         | 4.0  |

| 1.3.                            | DEVELOPER'S MANUAL, VOLUME 1: BASIC ARCHITECTURE  OVERVIEW OF THE INTEL ARCHITECTURE SOFTWARE       | 1-2  |

| 1.3.                            | DEVELOPER'S MANUAL, VOLUME 3: SYSTEM PROGRAMMING GUIDE                                              | 12   |

| 1.4.                            | NOTATIONAL CONVENTIONS                                                                              |      |

| 1. <del>4</del> .<br>1.4.1.     | Bit and Byte Order.                                                                                 |      |

| 1. <del>4</del> .1.<br>1.4.2.   | Reserved Bits and Software Compatibility                                                            | 1-5  |

| 1.4.3.                          | Instruction Operands                                                                                |      |

| 1.4.4.                          | Hexadecimal and Binary Numbers                                                                      |      |

| 1.4.5.                          | Segmented Addressing                                                                                |      |

| 1.4.6.                          | Exceptions                                                                                          |      |

| 1.5.                            | RELATED LITERATURE                                                                                  | 1-8  |

|                                 |                                                                                                     |      |

| CHAPT                           | ER 2                                                                                                |      |

| INSTRU                          | ICTION FORMAT                                                                                       |      |

| 2.1.                            | GENERAL INSTRUCTION FORMAT                                                                          | 2-1  |

| 2.2.                            | INSTRUCTION PREFIXES                                                                                | 2-1  |

| 2.3.                            | OPCODE                                                                                              |      |

| 2.4.                            | MODR/M AND SIB BYTES                                                                                | 2-2  |

| 2.5.                            | DISPLACEMENT AND IMMEDIATE BYTES                                                                    | 2-3  |

| 2.6.                            | ADDRESSING-MODE ENCODING OF MODR/M AND SIB BYTES                                                    | 2-3  |

| OLLADT                          | ED 4                                                                                                |      |

| CHAPT                           |                                                                                                     |      |

| 11 <b>13   KU</b><br>3.1.       | ICTION SET REFERENCE INTERPRETING THE INSTRUCTION REFERENCE PAGES                                   | 2.4  |

| 3.1.<br>3.1.1.                  |                                                                                                     |      |

| 3.1.1.<br>3.1.1.1.              | Instruction Format                                                                                  |      |

| 3.1.1.1.<br>3.1.1.2.            | Opcode Column                                                                                       |      |

| 3.1.1.2.<br>3.1.1.3.            | Description Column                                                                                  |      |

| 3.1.1.3.<br>3.1.1.4.            | Description                                                                                         |      |

| 3.1.1. <del>4</del> .<br>3.1.2. | Operation.                                                                                          |      |

| 3.1.2.<br>3.1.3.                | Flags Affected                                                                                      |      |

| 3.1.3.<br>3.1.4.                | FPU Flags Affected                                                                                  |      |

| 3.1. <del>4</del> .<br>3.1.5.   | Protected Mode Exceptions.                                                                          |      |

| 3.1.6.                          | Real-Address Mode Exceptions                                                                        |      |

| 3.1.7.                          | Virtual-8086 Mode Exceptions                                                                        |      |

| 3.1.8.                          | Floating-Point Exceptions                                                                           |      |

| 3.2.                            | INSTRUCTION REFERENCE                                                                               |      |

| 0.2.                            | AAA—ASCII Adjust After Addition                                                                     |      |

|                                 | AAD—ASCII Adjust AX Before Division.                                                                |      |

|                                 | AAD—ASCII Adjust AX After Multiply                                                                  |      |

|                                 | AAS—ASCII Adjust AX After Multiply                                                                  |      |

|                                 |                                                                                                     |      |

|                                 | ADD Add with Carry                                                                                  |      |

|                                 | ADD—Add                                                                                             | 3-1/ |

| AND—Logical AND                                          | 3-19  |

|----------------------------------------------------------|-------|

| ARPL—Adjust RPL Field of Segment Selector                | 3-21  |

| BOUND—Check Array Index Against Bounds                   |       |

| BSF—Bit Scan Forward                                     |       |

| BSR—Bit Scan Reverse                                     |       |

| BSWAP—Byte Swap                                          |       |

| BT—Bit Test.                                             |       |

| BTC—Bit Test and Complement                              |       |

| BTR—Bit Test and Reset                                   |       |

| BTS—Bit Test and Set.                                    |       |

| CALL—Call Procedure.                                     |       |

| CBW/CWDE—Convert Byte to Word/Convert Word to Doubleword |       |

|                                                          |       |

| CDQ—Convert Double to Quad                               |       |

| CLC—Clear Carry Flag                                     |       |

| CLD—Clear Direction Flag                                 |       |

| CLI—Clear Interrupt Flag                                 |       |

| CLTS—Clear Task-Switched Flag in CR0                     |       |

| CMC—Complement Carry Flag                                |       |

| CMOVcc—Conditional Move                                  |       |

| CMP—Compare Two Operands                                 |       |

| CMPS/CMPSB/CMPSW/CMPSD—Compare String Operands           |       |

| CMPXCHG—Compare and Exchange                             |       |

| CMPXCHG8B—Compare and Exchange 8 Bytes                   | 3-68  |

| CPUID—CPU Identification                                 | 3-70  |

| CWD/CDQ—Convert Word to Doubleword/Convert Doubleword    |       |

| to Quadword                                              | 3-77  |

| CWDE—Convert Word to Doubleword                          | 3-78  |

| DAA—Decimal Adjust AL after Addition                     | 3-79  |

| DAS—Decimal Adjust AL after Subtraction                  |       |

| DEC—Decrement by 1                                       |       |

| DIV—Unsigned Divide                                      |       |

| EMMS—Empty MMX™ State                                    |       |

| ENTER—Make Stack Frame for Procedure Parameters          |       |

| F2XM1—Compute 2x–1                                       |       |

| FABS—Absolute Value                                      |       |

| FADD/FADDP/FIADD—Add                                     |       |

| FBLD—Load Binary Coded Decimal                           |       |

| FBSTP—Store BCD Integer and Pop                          |       |

| FCHS—Change Sign                                         |       |

| FCLEX/FNCLEX—Clear Exceptions                            |       |

| FCMOVcc—Floating-Point Conditional Move                  |       |

| FCOM/FCOMP/FCOMPP—Compare Real                           |       |

|                                                          | 3-109 |

| FCOMI/FCOMIP/ FUCOMI/FUCOMIP—Compare Real and Set EFLAGS | 2 440 |

|                                                          |       |

| FCOS—Cosine                                              |       |

| FDECSTP—Decrement Stack-Top Pointer                      |       |

| FDIV/FDIVP/FIDIV—Divide                                  | კ-118 |

|                                              | PAGE  |

|----------------------------------------------|-------|

| FDIVR/FDIVRP/FIDIVR—Reverse Divide           | 3-122 |

| FFREE—Free Floating-Point Register           | 3-126 |

| FICOM/FICOMP—Compare Integer                 |       |

| FILD—Load Integer                            |       |

| FINCSTP—Increment Stack-Top Pointer          |       |

| FINIT/FNINIT—Initialize Floating-Point Unit  |       |

| FIST/FISTP—Store Integer                     |       |

| FLD—Load Real                                |       |

| FLD1/FLDL2T/FLDL2E/FLDPI/FLDLG2/FLDLN2/FLDZ— |       |

| Load Constant                                | 3-139 |

| FLDCW—Load Control Word                      |       |

| FLDENV—Load FPU Environment                  |       |

| FMUL/FMULP/FIMUL—Multiply                    |       |

| FNOP—No Operation                            |       |

| FPATAN—Partial Arctangent                    |       |

| FPATAN—Partial Arctangent                    |       |

| FPREM1—Partial Remainder                     |       |

| FPTAN—Partial Tangent                        |       |

| FRNDINT—Round to Integer                     |       |

| FRSTOR—Restore FPU State.                    |       |

| FSAVE/FNSAVE—Store FPU State                 |       |

| FSCALE—Scale                                 |       |

| FSIN—Sine                                    |       |

| FSINCOS—Sine and Cosine                      |       |

| FSQRT—Square Root                            |       |

| FST/FSTP—Store Real                          |       |

| FSTCW/FNSTCW—Store Control Word              |       |

| FSTENV/FNSTENV—Store FPU Environment         |       |

| FSTSW/FNSTSW—Store Status Word               |       |

| FSUB/FSUBP/FISUB—Subtract                    |       |

| FSUBR/FSUBRP/FISUBR—Reverse Subtract         |       |

| FTST—TEST                                    |       |

| FUCOM/FUCOMP/FUCOMPP—Unordered Compare Real  |       |

| FWAIT—Wait                                   |       |

| FXAM—Examine                                 |       |

| FXCH—Exchange Register Contents              |       |

| FXTRACT—Extract Exponent and Significand     |       |

| FYL2X—Compute y * log2x                      |       |

| FYL2XP1—Compute y * log2(x +1)               |       |

| HLT—Halt                                     |       |

| IDIV—Signed Divide                           |       |

| IMUL—Signed Multiply                         |       |

| IN—Input from Port                           |       |

| INC—Increment by 1                           |       |

| INS/INSB/INSW/INSD—Input from Port to String |       |

| INT n/INTO/INT 3—Call to Interrupt Procedure |       |

| INVD—Invalidate Internal Caches              |       |

|                                              | _     |

|                                                           | IAGE   |

|-----------------------------------------------------------|--------|

| INVLPG—Invalidate TLB Entry                               | .3-232 |

| IRET/IRETD—Interrupt Return                               | .3-233 |

| Jcc—Jump if Condition Is Met                              | .3-241 |

| JMP—Jump                                                  |        |

| LAHF—Load Status Flags into AH Register                   |        |

| LAR—Load Access Rights Byte                               |        |

| LDS/LES/LFS/LGS/LSS—Load Far Pointer                      |        |

| LEA—Load Effective Address                                |        |

| LEAVE—High Level Procedure Exit                           | .3-261 |

| LES—Load Full Pointer                                     | .3-263 |

| LFS—Load Full Pointer                                     |        |

| LGDT/LIDT—Load Global/Interrupt Descriptor Table Register |        |

| LGS—Load Full Pointer                                     | .3-267 |

| LLDT—Load Local Descriptor Table Register                 | .3-268 |

| LIDT—Load Interrupt Descriptor Table Register             | .3-270 |

| LMSW—Load Machine Status Word                             | .3-271 |

| LOCK—Assert LOCK# Signal Prefix                           | .3-273 |

| LODS/LODSB/LODSW/LODSD—Load String                        | .3-275 |

| LOOP/LOOPcc—Loop According to ECX Counter                 | .3-278 |

| LSL—Load Segment Limit                                    | .3-280 |

| LSS—Load Full Pointer                                     |        |

| LTR—Load Task Register                                    | .3-284 |

| MOV—Move                                                  |        |

| MOV—Move to/from Control Registers                        |        |

| MOV—Move to/from Debug Registers                          | .3-293 |

| MOVD—Move 32 Bits                                         |        |

| MOVQ—Move 64 Bits                                         | .3-297 |

| MOVS/MOVSB/MOVSW/MOVSD—Move Data from String to String    |        |

| MOVSX—Move with Sign-Extension                            | .3-302 |

| MOVZX—Move with Zero-Extend                               | .3-304 |

| MUL—Unsigned Multiply                                     |        |

| NEG—Two's Complement Negation                             |        |

| NOP—No Operation                                          |        |

| NOT—One's Complement Negation                             |        |

| OR—Logical Inclusive OR                                   | .3-313 |

| OUT—Output to Port                                        |        |

| OUTS/OUTSB/OUTSW/OUTSD—Output String to Port              |        |

| PACKSSWB/PACKSSDW—Pack with Signed Saturation             |        |

| PACKUSWB—Pack with Unsigned Saturation                    |        |

| PADDB/PADDW/PADDD—Packed Add                              |        |

| PADDSB/PADDSW—Packed Add with Saturation                  |        |

| PADDUSB/PADDUSW—Packed Add Unsigned with Saturation       |        |

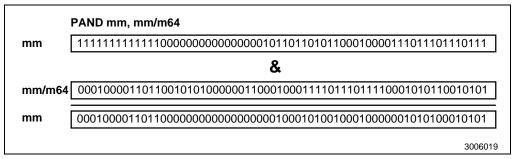

| PAND—Logical AND                                          |        |

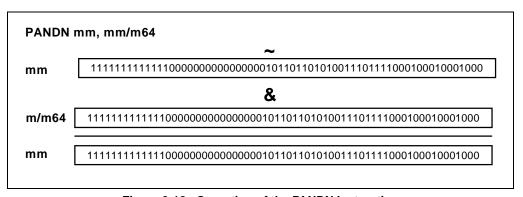

| PANDN—Logical AND NOT                                     | .3-336 |

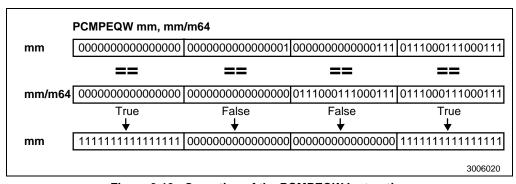

| PCMPEQB/PCMPEQW/PCMPEQD—Packed Compare for Equal          |        |

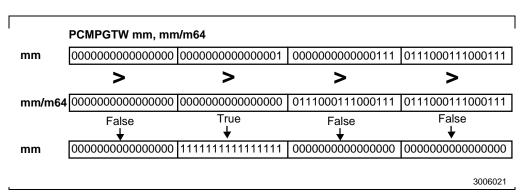

| PCMPGTB/PCMPGTW/PCMPGTD—Packed Compare for                |        |

| Greater Than                                              | 3-3/1  |

|                                                             | PAGE  |

|-------------------------------------------------------------|-------|

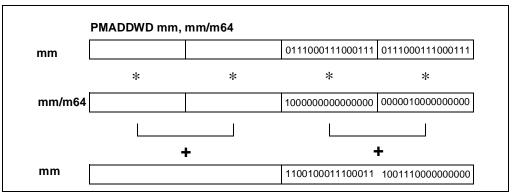

| PMADDWD—Packed Multiply and Add                             | 3-344 |

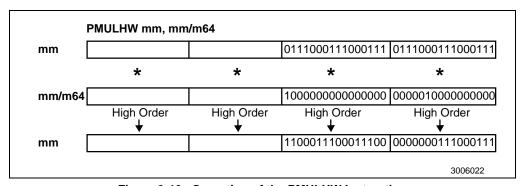

| PMULHW—Packed Multiply High                                 | 3-346 |

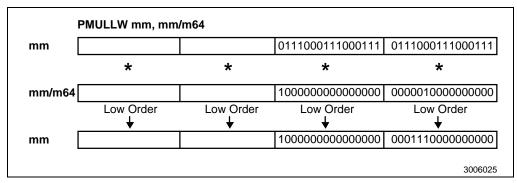

| PMULLW—Packed Multiply Low                                  |       |

| POP—Pop a Value from the Stack                              | 3-350 |

| POPA/POPAD—Pop All General-Purpose Registers                |       |

| POPF/POPFD—Pop Stack into EFLAGS Register                   |       |

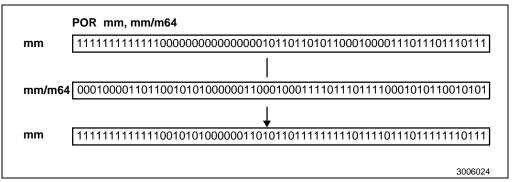

| POR—Bitwise Logical OR                                      | 3-359 |

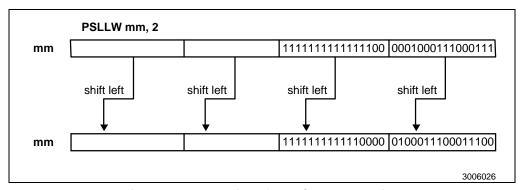

| PSLLW/PSLLD/PSLLQ—Packed Shift Left Logical                 | 3-361 |

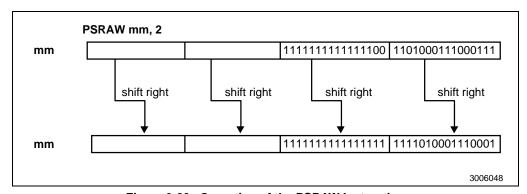

| PSRAW/PSRAD—Packed Shift Right Arithmetic                   | 3-364 |

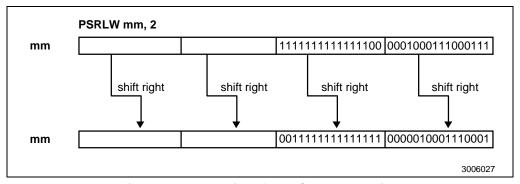

| PSRLW/PSRLD/PSRLQ—Packed Shift Right Logical                | 3-367 |

| PSUBB/PSUBW/PSUBD—Packed Subtract                           |       |

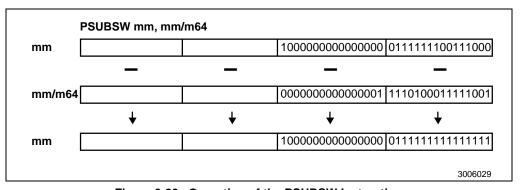

| PSUBSB/PSUBSW—Packed Subtract with Saturation               | 3-373 |

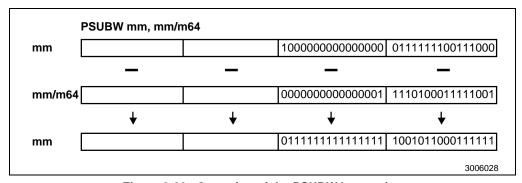

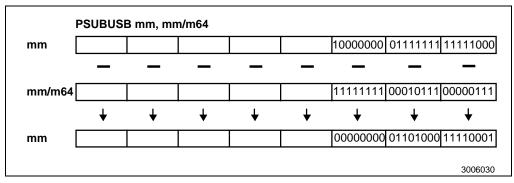

| PSUBUSB/PSUBUSW—Packed Subtract Unsigned with Saturation    | 3-376 |

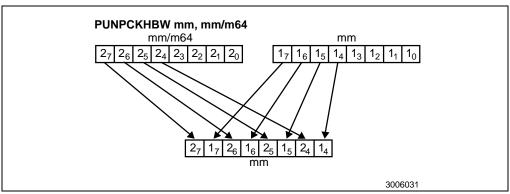

| PUNPCKHBW/PUNPCKHWD/PUNPCKHDQ—                              |       |

| Unpack High Packed Data                                     | 3-379 |

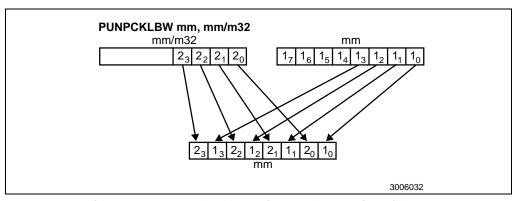

| PUNPCKLBW/PUNPCKLWD/PUNPCKLDQ—                              |       |

| Unpack Low Packed Data                                      | 3-382 |

| PUSH—Push Word or Doubleword Onto the Stack                 | 3-385 |

| PUSHA/PUSHAD—Push All General-Purpose Registers             | 3-388 |

| PUSHF/PUSHFD—Push EFLAGS Register onto the Stack            | 3-390 |

| PXOR—Logical Exclusive OR                                   | 3-392 |

| RCL/RCR/ROL/ROR-—Rotate                                     | 3-394 |

| RDMSR—Read from Model Specific Register                     | 3-399 |

| RDPMC—Read Performance-Monitoring Counters                  | 3-401 |

| RDTSC—Read Time-Stamp Counter                               | 3-403 |

| REP/REPE/REPZ/REPNE /REPNZ—Repeat String Operation Prefix . | 3-404 |

| RET—Return from Procedure                                   | 3-407 |

| ROL/ROR—Rotate                                              | 3-413 |

| RSM—Resume from System Management Mode                      | 3-414 |

| SAHF—Store AH into Flags                                    | 3-415 |

| SAL/SAR/SHL/SHR—Shift                                       | 3-416 |

| SBB—Integer Subtraction with Borrow                         | 3-420 |

| SCAS/SCASB/SCASW/SCASD—Scan String                          | 3-422 |

| SETcc—Set Byte on Condition                                 |       |

| SGDT/SIDT—Store Global/Interrupt Descriptor Table Register  | 3-427 |

| SHL/SHR—Shift Instructions                                  | 3-429 |

| SHLD—Double Precision Shift Left                            | 3-430 |

| SHRD—Double Precision Shift Right                           |       |

| SIDT—Store Interrupt Descriptor Table Register              | 3-434 |

| SLDT—Store Local Descriptor Table Register                  |       |

| SMSW—Store Machine Status Word                              | 3-437 |

| STC—Set Carry Flag                                          |       |

| STD—Set Direction Flag                                      |       |

| STI—Set Interrupt Flag                                      |       |

| STOS/STOSB/STOSW/STOSD—Store String                         |       |

| STR—Store Task Register                                     |       |

| SUB—Subtract                                                | 3-448 |

|                  | TEST—Logical Compare                                                                |            |

|------------------|-------------------------------------------------------------------------------------|------------|

|                  | UD2—Undefined Instruction                                                           |            |

|                  | VERR, VERW—Verify a Segment for Reading or Writing                                  |            |

|                  | WAIT/FWAIT—Wait                                                                     |            |

|                  | WBINVD—Write Back and Invalidate Cache                                              | 3-456      |

|                  | WRMSR—Write to Model Specific Register                                              | 3-458      |

|                  | XADD—Exchange and Add                                                               | 3-460      |

|                  | XCHG—Exchange Register/Memory with Register                                         |            |

|                  | XLAT/XLATB—Table Look-up Translation                                                |            |

|                  | XOR—Logical Exclusive OR                                                            |            |

| APPEN            | NDIX A                                                                              |            |

| OPCO             | DE MAP                                                                              |            |

| A.1.             | KEY TO ABBREVIATIONS                                                                |            |

| A.1.1.           | Codes for Addressing Method                                                         | A-1        |

| A.1.2.           | Codes for Operand Type                                                              | A-2        |

| A.1.3.           | Register Codes                                                                      | A-3        |

| A.2.             | ONE-BYTE OPCODE INTEGER INSTRUCTIONS                                                |            |

| A.3.<br>A.4.     | TWO-BYTE OPCODE INTEGER INSTRUCTIONSOPCODE EXTENSIONS FOR ONE- AND TWO-BYTE OPCODES | -A-c       |

| A.4.<br>A.5.     | ESCAPE OPCODE INSTRUCTIONS                                                          |            |

| A.5.1.           | Escape Opcodes with D8 as First Byte                                                |            |

| A.5.2.           | Escape Opcodes with D9 as First Byte                                                |            |

| A.5.3.           | Escape Opcodes with DA as First Byte                                                |            |

| A.5.4.           | Escape Opcodes with DB as First Byte                                                |            |

| A.5.5.           | Escape Opcodes with DC as First Byte                                                |            |

| A.5.6.           | Escape Opcodes with DD as First Byte                                                |            |

| A.5.7.           | Escape Opcodes with DE as First Byte                                                | A-22       |

| A.5.8.           | Escape Opcodes with DF As First Byte                                                | A-24       |

|                  | NDIX B                                                                              |            |

|                  | UCTION FORMATS AND ENCODINGS                                                        |            |

| B.1.             | MACHINE INSTRUCTION FORMAT                                                          |            |

| B.1.1.           | Reg Field (reg)                                                                     |            |

| B.1.2.           | Encoding of Operand Size Bit (w)                                                    |            |

| B.1.3.<br>B.1.4. | Sign Extend (s) Bit                                                                 | B-3        |

| B.1.4.           | Special-Purpose Register (eee) Field                                                | D-4        |

| B.1.6.           | Condition Test Field (tttn)                                                         | ۲-۱۰۰۰ R-۶ |

| B.1.7.           | Direction (d) Bit                                                                   |            |

| B.2.             | INTEGER INSTRUCTION FORMATS AND ENCODINGS                                           | B-6        |

| B.3.             | MMX™ INSTRUCTION FORMATS AND ENCODINGS                                              | B-19       |

| B.3.1.           | Granularity Field (gg)                                                              |            |

| B.3.2.           | MMX™ and General-Purpose Register Fields (mmxreg                                    |            |

|                  | and reg)                                                                            | B-19       |

| B.3.3.           | MMX™ Instruction Formats and Encodings Table                                        | B-20       |

| B.4.             | FLOATING-POINT INSTRUCTION FORMATS AND ENCODINGS                                    | B-24       |

### **TABLE OF FIGURES**

|              |                                                             | PAGE  |

|--------------|-------------------------------------------------------------|-------|

| Figure 1-1.  | Bit and Byte Order                                          | 1-5   |

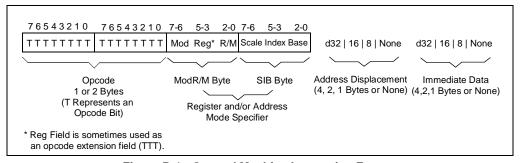

| Figure 2-1.  | Intel Architecture Instruction Format                       | 2-1   |

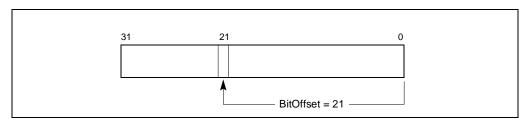

| Figure 3-1.  | Bit Offset for BIT[EAX,21]                                  | 3-7   |

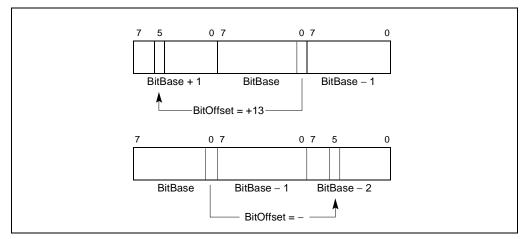

| Figure 3-2.  | Memory Bit Indexing                                         |       |

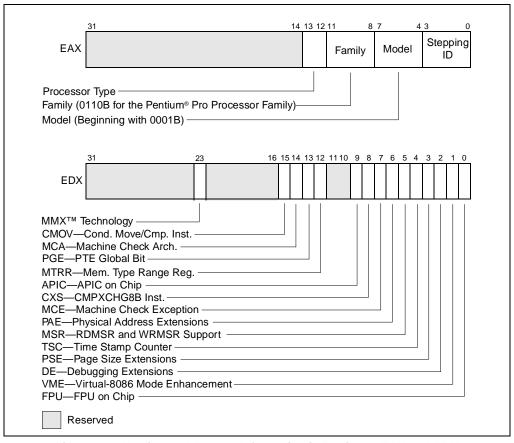

| Figure 3-3.  | Version and Feature Information in Registers EAX and EDX    | 3-71  |

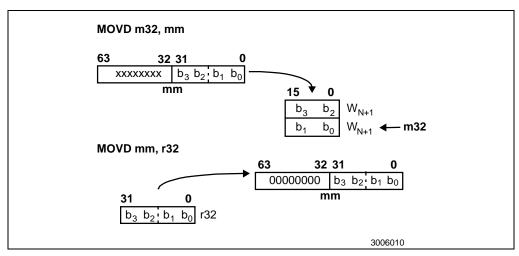

| Figure 3-4.  | Operation of MOVD Instruction                               |       |

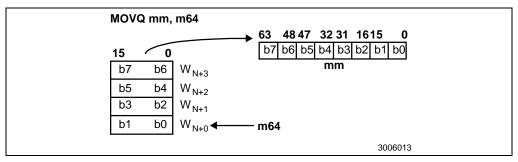

| Figure 3-5.  | Operation of the MOVQ Instructions                          |       |

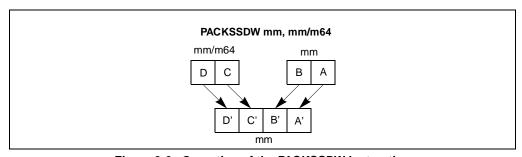

| Figure 3-6.  | Operation of the PACKSSDW Instruction                       | 3-320 |

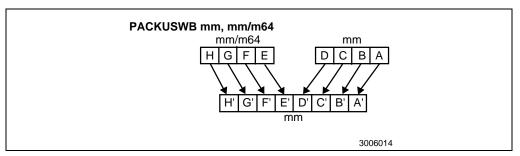

| Figure 3-7.  | Operation of the PACKUSWB Instruction                       | 3-323 |

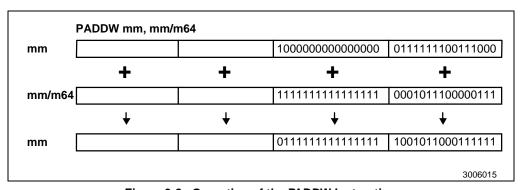

| Figure 3-8.  | Operation of the PADDW Instruction                          | 3-325 |

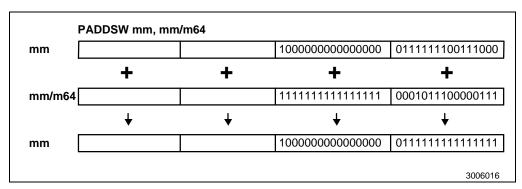

| Figure 3-9.  | Operation of the PADDSW Instruction                         | 3-328 |

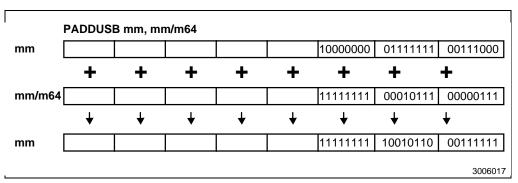

| Figure 3-10. | Operation of the PADDUSB Instruction                        | 3-331 |

| Figure 3-11. | Operation of the PAND Instruction                           | 3-334 |

| Figure 3-12. | Operation of the PANDN Instruction                          | 3-336 |

| Figure 3-13. | Operation of the PCMPEQW Instruction                        | 3-338 |

| Figure 3-14. | Operation of the PCMPGTW Instruction                        |       |

| Figure 3-15. | Operation of the PMADDWD Instruction                        |       |

| Figure 3-16. | Operation of the PMULHW Instruction                         |       |

| Figure 3-17. | Operation of the PMULLW Instruction                         |       |

| Figure 3-18. | Operation of the POR Instruction                            |       |

| Figure 3-19. | Operation of the PSLLW Instruction                          |       |

| Figure 3-20. | Operation of the PSRAW Instruction                          |       |

| Figure 3-21. | Operation of the PSRLW Instruction                          |       |

| Figure 3-22. | Operation of the PSUBW Instruction                          |       |

| Figure 3-23. | Operation of the PSUBSW Instruction                         |       |

| Figure 3-24. | Operation of the PSUBUSB Instruction                        | 3-376 |

| Figure 3-25. | High-Order Unpacking and Interleaving of Bytes              |       |

|              | With the PUNPCKHBW Instruction                              | 3-379 |

| Figure 3-26. | Low-Order Unpacking and Interleaving of Bytes               |       |

|              | With the PUNPCKLBW Instruction                              |       |

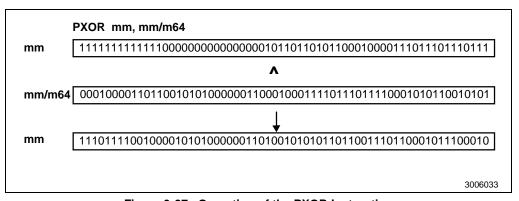

| Figure 3-27. | Operation of the PXOR Instruction                           |       |

| Figure A-1.  | ModR/M Byte nnn Field (Bits 5, 4, and 3)                    |       |

| Figure B-1.  | General Machine Instruction Format                          |       |

| Figure B-2.  | Key to Codes for MMX <sup>™</sup> Data Type Cross-Reference | B-20  |

### **TABLE OF TABLES**

|             |                                                                        | PAGE   |

|-------------|------------------------------------------------------------------------|--------|

| Table 2-1.  | 16-Bit Addressing Forms with the ModR/M Byte                           | 2-4    |

| Table 2-2.  | 32-Bit Addressing Forms with the ModR/M Byte                           |        |

| Table 2-3.  | 32-Bit Addressing Forms with the SIB Byte                              | 2-6    |

| Table 3-1.  | Register Encodings Associated with the +rb, +rw, and +rd Nomenclature. | 3-2    |

| Table 3-2.  | Exception Mnemonics, Names, and Vector Numbers                         | 3-9    |

| Table 3-3.  | Floating-Point Exception Mnemonics and Names                           | 3-10   |

| Table 3-4.  | Information Returned by CPUID Instruction                              | 3-70   |

| Table 3-5.  | Processor Type Field                                                   | 3-72   |

| Table 3-6.  | Feature Flags Returned in EDX Register                                 | 3-72   |

| Table 3-7.  | Encoding of Cache and TLB Descriptors                                  | 3-74   |

| Table A-1.  | One-Byte Opcode Map1                                                   | A-4    |

| Table A-2.  | Two Byte Opcode Map (First byte is 0FH)1                               |        |

| Table A-3.  | Opcode Extensions for One- and Two-Byte Opcodes by Group Number1       | A-8    |

| Table A-4.  | D8 Opcode Map When ModR/M Byte is Within 00H to BFH1                   | . A-10 |

| Table A-5.  | D8 Opcode Map When ModR/M Byte is Outside 00H to BFH1                  | . A-11 |

| Table A-6.  | D9 Opcode Map When ModR/M Byte is Within 00H to BFH1                   | . A-12 |

| Table A-7.  | D9 Opcode Map When ModR/M Byte is Outside 00H to BFH1                  |        |

| Table A-8.  | DA Opcode Map When ModR/M Byte is Within 00H to BFH1                   | . A-14 |

| Table A-9.  | DA Opcode Map When ModR/M Byte is Outside 00H to BFH1                  | . A-15 |

| Table A-10. | DB Opcode Map When ModR/M Byte is Within 00H to BFH1                   | . A-16 |

| Table A-11. | DB Opcode Map When ModR/M Byte is Outside 00H to BFH1                  | . A-17 |

| Table A-12. | DC Opcode Map When ModR/M Byte is Within 00H to BFH1                   | . A-18 |

| Table A-13. | DC Opcode Map When ModR/M Byte is Outside 00H to BFH1                  |        |

| Table A-14. | DD Opcode Map When ModR/M Byte is Within 00H to BFH1                   |        |

| Table A-15. | DD Opcode Map When ModR/M Byte is Outside 00H to BFH1                  |        |

| Table A-16. | DE Opcode Map When ModR/M Byte is Within 00H to BFH1                   | . A-22 |

| Table A-17. | DE Opcode Map When ModR/M Byte is Outside 00H to BFH1                  |        |

| Table A-18. | DF Opcode Map When ModR/M Byte is Within 00H to BFH1                   |        |

| Table A-19. | DF Opcode Map When ModR/M Byte is Outside 00H to BFH1                  |        |

| Table B-1.  | Special Fields Within Instruction Encodings                            | B-2    |

| Table B-2.  | Encoding of reg Field When w Field is Not Present in Instruction       |        |

| Table B-3.  | Encoding of reg Field When w Field is Present in Instruction           |        |

| Table B-4.  | Encoding of Operand Size (w) Bit                                       |        |

| Table B-5.  | Encoding of Sign-Extend (s) Bit                                        |        |

| Table B-6.  | Encoding of the Segment Register (sreg) Field                          | B-4    |

| Table B-7.  | Encoding of Special-Purpose Register (eee) Field                       | B-4    |

| Table B-8.  | Encoding of Conditional Test (tttn) Field                              | B-5    |

| Table B-9.  | Encoding of Operation Direction (d) Bit                                | B-6    |

| Table B-10. | Integer Instruction Formats and Encodings                              |        |

| Table B-11. | Encoding of Granularity of Data Field (gg)                             |        |

| Table B-12. | Encoding of the MMX <sup>™</sup> Register Field (mmxreg)               | . B-19 |

| Table B-13. | Encoding of the General-Purpose Register Field (reg) When              |        |

|             | Used in MMX™ Instructions                                              | . B-20 |

| Table B-14. | MMX <sup>™</sup> Instruction Formats and Encodings                     | . B-20 |

| Table B-15. | General Floating-Point Instruction Formats                             |        |

| Table B-16. | Floating-Point Instruction Formats and Encodings                       | . B-25 |

int<sub>el®</sub>

1

## **About This Manual**

## CHAPTER 1 ABOUT THIS MANUAL

The Intel Architecture Software Developer's Manual, Volume 2: Instruction Set Reference (Order Number 243191) is part of a three-volume set that describes the architecture and programming environment of all Intel Architecture processors. The other two volumes in this set are:

- The Intel Architecture Software Developer's Manual, Volume 1: Basic Architecture (Order Number 243190).

- The Intel Architecture Software Developer's Manual, Volume 3: System Programing Guide (Order Number 243192).

The Intel Architecture Software Developer's Manual, Volume 1, describes the basic architecture and programming environment of an Intel Architecture processor; the Intel Architecture Software Developer's Manual, Volume 2, describes the instructions set of the processor and the opcode structure. These two volumes are aimed at application programmers who are writing programs to run under existing operating systems or executives. The Intel Architecture Software Developer's Manual, Volume 3, describes the operating-system support environment of an Intel Architecture processor, including memory management, protection, task management, interrupt and exception handling, and system management mode. It also provides Intel Architecture processor compatibility information. This volume is aimed at operating-system and BIOS designers and programmers.

# 1.1. OVERVIEW OF THE INTEL ARCHITECTURE SOFTWARE DEVELOPER'S MANUAL, VOLUME 2: INSTRUCTION SET REFERENCE

The contents of this manual are as follows:

**Chapter 1** — **About This Manual.** Gives an overview of all three volumes of the *Intel Architecture Software Developer's Manual*. It also describes the notational conventions in these manuals and lists related Intel manuals and documentation of interest to programmers and hardware designers.

**Chapter 2** — **Instruction Format.** Describes the machine-level instruction format used for all Intel Architecture instructions and gives the allowable encodings of prefixes, the operand-identifier byte (ModR/M byte), the addressing-mode specifier byte (SIB byte), and the displacement and immediate bytes.

Chapter 3 — Instruction Set Reference. Describes each of the Intel Architecture instructions in detail, including an algorithmic description of operations, the effect on flags, the effect of operand- and address-size attributes, and the exceptions that may be generated. The instructions are arranged in alphabetical order. The MMX<sup>TM</sup> instructions are included in this chapter.

**Appendix A** — **Opcode Map.** Gives an opcode map for the Intel Architecture instruction set.

**Appendix B** — **Instruction Formats and Encodings.** Gives the binary encoding of each form of each Intel Architecture instruction.

# 1.2. OVERVIEW OF THE INTEL ARCHITECTURE SOFTWARE DEVELOPER'S MANUAL, VOLUME 1: BASIC ARCHITECTURE

The contents of the Intel Architecture Software Developer's Manual, Volume 1, are as follows:

**Chapter 1** — **About This Manual.** Gives an overview of all three volumes of the *Intel Architecture Software Developer's Manual*. It also describes the notational conventions in these manuals and lists related Intel manuals and documentation of interest to programmers and hardware designers.

**Chapter 2** — **Introduction to the Intel Architecture.** Introduces the Intel Architecture and the families of Intel processors that are based on this architecture. It also gives an overview of the common features found in these processors and brief history of the Intel Architecture.

**Chapter 3** — **Basic Execution Environment.** Introduces the models of memory organization and describes the register set used by applications.

**Chapter 4** — **Procedure Calls, Interrupts, and Exceptions.** Describes the procedure stack and the mechanisms provided for making procedure calls and for servicing interrupts and exceptions.

**Chapter 5** — **Data Types and Addressing Modes.** Describes the data types and addressing modes recognized by the processor.

**Chapter 6** — **Instruction Set Summary.** Gives an overview of all the Intel Architecture instructions except those executed by the processor's floating-point unit. The instructions are presented in functionally related groups.

Chapter 7 — Floating-Point Unit. Describes the Intel Architecture floating-point unit, including the floating-point registers and data types; gives an overview of the floating-point instruction set; and describes the processor's floating-point exception conditions.

**Chapter 8** — **Programming with Intel MMX**<sup>TM</sup> **Technology.** Describes the Intel MMX technology, including MMX registers and data types, and gives an overview of the MMX instruction set.

**Chapter 9** — **Input/Output.** Describes the processor's I/O architecture, including I/O port addressing, the I/O instructions, and the I/O protection mechanism.

**Chapter 10** — **Processor Identification and Feature Determination.** Describes how to determine the CPU type and the features that are available in the processor.

**Appendix A** — **EFLAGS Cross-Reference.** Summaries how the Intel Architecture instructions affect the flags in the EFLAGS register.

**Appendix B** — **EFLAGS Condition Codes.** Summarizes how the conditional jump, move, and byte set on condition code instructions use the condition code flags (OF, CF, ZF, SF, and PF) in the EFLAGS register.

**Appendix C** — **Floating-Point Exceptions Summary.** Summarizes the exceptions that can be raised by floating-point instructions.

**Appendix D** — **Guidelines for Writing FPU Exception Handlers.** Describes how to design and write MS-DOS\* compatible exception handling facilities for FPU exceptions, including both software and hardware requirements and assembly-language code examples. This appendix also describes general techniques for writing robust FPU exception handlers.

# 1.3. OVERVIEW OF THE INTEL ARCHITECTURE SOFTWARE DEVELOPER'S MANUAL, VOLUME 3: SYSTEM PROGRAMMING GUIDE

The contents of the Intel Architecture Software Developer's Manual, Volume 3, are as follows:

**Chapter 1** — **About This Manual.** Gives an overview of all three volumes of the *Intel Architecture Software Developer's Manual*. It also describes the notational conventions in these manuals and lists related Intel manuals and documentation of interest to programmers and hardware designers.

Chapter 2 — System Architecture Overview. Describes the modes of operation of an Intel Architecture processor and the mechanisms provided in the Intel Architecture to support operating systems and executives, including the system-oriented registers and data structures and the system-oriented instructions. The steps necessary for switching between real-address and protected modes are also identified.

**Chapter 3**—**Protected-Mode Memory Management.** Describes the data structures, registers, and instructions that support segmentation and paging and explains how they can be used to implement a "flat" (unsegmented) memory model or a segmented memory model.

**Chapter 4** — **Protection.** Describes the support for page and segment protection provided in the Intel Architecture. This chapter also explains the implementation of privilege rules, stack switching, pointer validation, user and supervisor modes.

**Chapter 5** — **Interrupt and Exception Handling.** Describes the basic interrupt mechanisms defined in the Intel Architecture, shows how interrupts and exceptions relate to protection, and describes how the architecture handles each exception type. Reference information for each Intel Architecture exception is given at the end of this chapter.

**Chapter 6** — **Task Management.** Describes the mechanisms the Intel Architecture provides to support multitasking and inter-task protection.

**Chapter 7** — **Multiple Processor Management.** Describes the instructions and flags that support multiple processors with shared memory, memory ordering, and the advanced programmable interrupt controller (APIC).

**Chapter 8** — **Processor Management and Initialization.** Defines the state of an Intel Architecture processor and its floating-point unit after reset initialization. This chapter also explains how to set up an Intel Architecture processor for real-address mode operation and protected mode operation, and how to switch between modes.

Chapter 9 — Memory Cache Control. Describes the general concept of caching and the caching mechanisms supported by the Intel Architecture. This chapter also describes the memory type range registers (MTRRs) and how they can be used to map memory types of physical memory. MTRRs were introduced into the Intel Architecture with the Pentium<sup>®</sup> Pro processor.

Chapter 10 — MMX<sup>TM</sup> Technology System Programming Model. Describes those aspects of the Intel MMX technology that must be handled and considered at the system programming level, including task switching, exception handling, and compatibility with existing system environments.

**Chapter 11** — **System Management Mode (SMM).** Describes the Intel Architecture's system management mode (SMM), which can be used to implement power management functions.

**Chapter 12** — **Machine Check Architecture.** Describes the machine check architecture, which was introduced into the Intel Architecture with the Pentium processor.

**Chapter 13** — **Code Optimization.** Discusses general optimization techniques for programming an Intel Architecture processor.

Chapter 14 — Debugging and Performance Monitoring. Describes the debugging registers and other debug mechanism provided in the Intel Architecture. This chapter also describes the time-stamp counter and the performance monitoring counters.

**Chapter 15** — **8086 Emulation.** Describes the real-address and virtual-8086 modes of the Intel Architecture.

**Chapter 16** — **Mixing 16-Bit and 32-Bit Code.** Describes how to mix 16-bit and 32-bit code modules within the same program or task.

Chapter 17 — Intel Architecture Compatibility. Describes the programming differences between the Intel 286, Intel386<sup>TM</sup>, Intel486<sup>TM</sup>, Pentium, and Pentium Pro processors. The differences among the 32-bit Intel Architecture processors (the Intel386, Intel486, Pentium, and Pentium Pro processors) are described throughout the three volumes of the *Intel Architecture Software Developer's Manual*, as relevant to particular features of the architecture. This chapter provides a collection of all the relevant compatibility information for all Intel Architecture processors and also describes the basic differences with respect to the 16-bit Intel Architecture processors (the Intel 8086 and Intel 286 processors).

**Appendix A** — **Performance-Monitoring Counters.** Lists the events that can be counted with the performance-monitoring counters and the codes used to select these events.

**Appendix B** — **Model Specific Registers (MSRs).** Lists the MSRs available in the Pentium Pro processor and their functions.

### 1.4. NOTATIONAL CONVENTIONS

This manual uses special notation for data-structure formats, for symbolic representation of instructions, and for hexadecimal numbers. A review of this notation makes the manual easier to read.

### 1.4.1. Bit and Byte Order

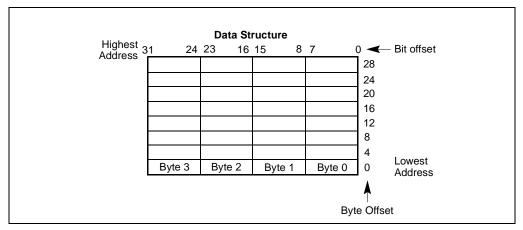

In illustrations of data structures in memory, smaller addresses appear toward the bottom of the figure; addresses increase toward the top. Bit positions are numbered from right to left. The numerical value of a set bit is equal to two raised to the power of the bit position. Intel Architecture processors is a "little endian" machines; this means the bytes of a word are numbered starting from the least significant byte. Figure 1-1 illustrates these conventions.

Figure 1-1. Bit and Byte Order

### 1.4.2. Reserved Bits and Software Compatibility

In many register and memory layout descriptions, certain bits are marked as **reserved**. When bits are marked as reserved, it is essential for compatibility with future processors that software treat these bits as having a future, though unknown, effect. The behavior of reserved bits should be regarded as not only undefined, but unpredictable. Software should follow these guidelines in dealing with reserved bits:

- Do not depend on the states of any reserved bits when testing the values of registers which contain such bits. Mask out the reserved bits before testing.

- Do not depend on the states of any reserved bits when storing to memory or to a register.

- Do not depend on the ability to retain information written into any reserved bits.

- When loading a register, always load the reserved bits with the values indicated in the documentation, if any, or reload them with values previously read from the same register.

#### NOTE

Avoid any software dependence upon the state of reserved bits in Intel Architecture registers. Depending upon the values of reserved register bits will make software dependent upon the unspecified manner in which the processor handles these bits. Depending upon reserved values risks incompatibility with future processors.

### 1.4.3. Instruction Operands

When instructions are represented symbolically, a subset of the Intel Architecture assembly language is used. In this subset, an instruction has the following format:

label: mnemonic argument1, argument2, argument3

#### where:

- A label is an identifier which is followed by a colon.

- A mnemonic is a reserved name for a class of instruction opcodes which have the same function.

- The operands *argument1*, *argument2*, and *argument3* are optional. There may be from zero to three operands, depending on the opcode. When present, they take the form of either literals or identifiers for data items. Operand identifiers are either reserved names of registers or are assumed to be assigned to data items declared in another part of the program (which may not be shown in the example).

When two operands are present in an arithmetic or logical instruction, the right operand is the source and the left operand is the destination.

### For example:

LOADREG: MOV EAX, SUBTOTAL

In this example LOADREG is a label, MOV is the mnemonic identifier of an opcode, EAX is the destination operand, and SUBTOTAL is the source operand. Some assembly languages put the source and destination in reverse order.

### 1.4.4. Hexadecimal and Binary Numbers

Base 16 (hexadecimal) numbers are represented by a string of hexadecimal digits followed by the character H (for example, F82EH). A hexadecimal digit is a character from the following set: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, and F.

Base 2 (binary) numbers are represented by a string of 1s and 0s, sometimes followed by the character B (for example, 1010B). The "B" designation is only used in situations where confusion as to the type of number might arise.

### 1.4.5. Segmented Addressing

The processor uses byte addressing. This means memory is organized and accessed as a sequence of bytes. Whether one or more bytes are being accessed, a byte address is used to locate the byte or bytes memory. The range of memory that can be addressed is called an **address space**.

The processor also supports segmented addressing. This is a form of addressing where a program may have many independent address spaces, called **segments**. For example, a program can keep its code (instructions) and stack in separate segments. Code addresses would always refer to the code space, and stack addresses would always refer to the stack space. The following notation is used to specify a byte address within a segment:

Segment-register:Byte-address

For example, the following segment address identifies the byte at address FF79H in the segment pointed by the DS register:

DS:FF79H

The following segment address identifies an instruction address in the code segment. The CS register points to the code segment and the EIP register contains the address of the instruction.

CS:EIP

### 1.4.6. Exceptions

An exception is an event that typically occurs when an instruction causes an error. For example, an attempt to divide by zero generates an exception. However, some exceptions, such as breakpoints, occur under other conditions. Some types of exceptions may provide error codes. An error code reports additional information about the error. An example of the notation used to show an exception and error code is shown below.

```

#PF(fault code)

```

This example refers to a page-fault exception under conditions where an error code naming a type of fault is reported. Under some conditions, exceptions which produce error codes may not be able to report an accurate code. In this case, the error code is zero, as shown below for a general-protection exception.

#GP(0)

See Chapter 5, *Interrupt and Exception Handling*, in the *Intel Architecture Software Developer's Manual, Volume 3*, for a list of exception mnemonics and their descriptions.

### 1.5. RELATED LITERATURE

The following books contain additional material related to Intel processors:

- Intel Pentium® Pro Processor Specification Update, Order Number 242689.

- Intel Pentium® Processor Specification Update, Order Number 242480.

- AP-485, Intel Processor Identification and the CPUID Instruction, Order Number 241618.

- AP-578, Software and Hardware Considerations for FPU Exception Handlers for Intel Architecture Processors, Order Number 242415-001.

- Pentium® Pro Processor Family Developer's Manual, Volume 1: Specifications, Order Number 242690-001.

- Pentium® Processor Family Developer's Manual, Order Number 241428.

- Intel486<sup>TM</sup> Microprocessor Data Book, Order Number 240440.

- Intel486<sup>TM</sup> SX CPU/Intel487<sup>TM</sup> SX Math Coprocessor Data Book, Order Number 240950.

- Intel486<sup>TM</sup> DX2 Microprocessor Data Book, Order Number 241245.

- Intel486™ Microprocessor Product Brief Book, Order Number 240459.

- *Intel386™ Processor Hardware Reference Manual*, Order Number 231732.

- Intel386<sup>TM</sup> Processor System Software Writer's Guide, Order Number 231499.

- Intel386<sup>TM</sup> High-Performance 32-Bit CHMOS Microprocessor with Integrated Memory Management, Order Number 231630.

- 376 Embedded Processor Programmer's Reference Manual, Order Number 240314.

- 80387 DX User's Manual Programmer's Reference, Order Number 231917.

- 376 High-Performance 32-Bit Embedded Processor, Order Number 240182.

- *Intel386*<sup>TM</sup> *SX Microprocessor*, Order Number 240187.

- *Microprocessor and Peripheral Handbook* (Vol. 1), Order Number 230843.

- AP-528, Optimizations for Intel's 32-Bit Processors, Order Number 242816-001.

int<sub>el®</sub>

2

### **Instruction Format**

## CHAPTER 2 INSTRUCTION FORMAT

This chapter describes the instruction format for all Intel Architecture processors.

### 2.1. GENERAL INSTRUCTION FORMAT

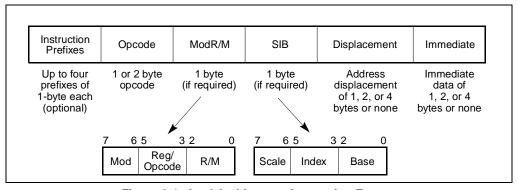

All Intel Architecture instruction encodings are subsets of the general instruction format shown in Figure 2-1. Instructions consist of optional instruction prefixes (in any order), one or two primary opcode bytes, an addressing-form specifier (if required) consisting of the ModR/M byte and sometimes the SIB (Scale-Index-Base) byte, a displacement (if required), and an immediate data field (if required).

Figure 2-1. Intel Architecture Instruction Format

### 2.2. INSTRUCTION PREFIXES

The instruction prefixes are divided into four groups, each with a set of allowable prefix codes:

- Lock and repeat prefixes.

- F0H—LOCK prefix.

- F2H—REPNE/REPNZ prefix (used only with string instructions).

- F3H—REP prefix (used only with string instructions).

- F3H—REPE/REPZ prefix (used only with string instructions).

- Segment override.

- 2EH—CS segment override prefix.

- 36H—SS segment override prefix.

#### INSTRUCTION FORMAT

- 3EH—DS segment override prefix.

- 26H—ES segment override prefix.

- 64H—FS segment override prefix.

- 65H—GS segment override prefix.

- Operand-size override, 66H

- Address-size override, 67H

For each instruction, one prefix may be used from each of these groups and be placed in any order. The effect of redundant prefixes (more than one prefix from a group) is undefined and may vary from processor to processor.

### 2.3. OPCODE

The primary opcode is either 1 or 2 bytes. An additional 3-bit opcode field is sometimes encoded in the ModR/M byte. Smaller encoding fields can be defined within the primary opcode. These fields define the direction of the operation, the size of displacements, the register encoding, condition codes, or sign extension. The encoding of fields in the opcode varies, depending on the class of operation.

### 2.4. MODR/M AND SIB BYTES

Most instructions that refer to an operand in memory have an addressing-form specifier byte (called the ModR/M byte) following the primary opcode. The ModR/M byte contains three fields of information:

- The *mod* field combines with the r/m field to form 32 possible values: eight registers and 24 addressing modes.

- The *reg/opcode* field specifies either a register number or three more bits of opcode information. The purpose of the reg/opcode field is specified in the primary opcode.

- The *r/m* field can specify a register as an operand or can be combined with the mod field to encode an addressing mode.

Certain encodings of the ModR/M byte require a second addressing byte, the SIB byte, to fully specify the addressing form. The base-plus-index and scale-plus-index forms of 32-bit addressing require the SIB byte. The SIB byte includes the following fields:

- The *scale* field specifies the scale factor.

- The *index* field specifies the register number of the index register.

- The *base* field specifies the register number of the base register.

See Section 2.6., "Addressing-Mode Encoding of ModR/M and SIB Bytes", for the encodings of the ModR/M and SIB bytes.

### 2.5. DISPLACEMENT AND IMMEDIATE BYTES

Some addressing forms include a displacement immediately following either the ModR/M or SIB byte. If a displacement is required, it can be 1, 2, or 4 bytes.

If the instruction specifies an immediate operand, the operand always follows any displacement bytes. An immediate operand can be 1, 2 or 4 bytes.

### 2.6. ADDRESSING-MODE ENCODING OF MODR/M AND SIB BYTES

The values and the corresponding addressing forms of the ModR/M and SIB bytes are shown in Tables 2-1 through 2-3. The 16-bit addressing forms specified by the ModR/M byte are in Table 2-1, and the 32-bit addressing forms specified by the ModR/M byte are in Table 2-2. Table 2-3 shows the 32-bit addressing forms specified by the SIB byte.

In Tables 2-1 and 2-2, the first column (labeled "Effective Address") lists 32 different effective addresses that can be assigned to one operand of an instruction by using the Mod and R/M fields of the ModR/M byte. The first 24 give the different ways of specifying a memory location; the last 8 (specified by the Mod field encoding 11B) give the ways of specifying the general purpose and MMX registers. Each of the register encodings list four possible registers. For example, the first register-encoding (selected by the R/M field encoding of 000B) indicates the general-purpose registers EAX, AX or AL, or the MMX register MM0. Which of these four registers is used is determined by the opcode byte and the operand-size attribute, which select either the EAX register (32 bits) or AX register (16 bits).

The second and third columns in Tables 2-1 and 2-2 gives the binary encodings of the Mod and R/M fields in the ModR/M byte, respectively, required to obtain the associated effective address listed in the first column. All 32 possible combinations of the Mod and R/M fields are listed.

Across the top of Tables 2-1 and 2-2, the 8 possible values of the 3-bit Reg/Opcode field are listed, in decimal (fifth row from top) and in binary (sixth row from top). The sixth row is labeled "REG=" which represents the use of these 3 bits to give the location of a second operand, which must be a general-purpose register or an MMX register. If the instruction does not require a second operand to be specified, then the 3 bits of the Reg/Opcode field may be used as an extension of the opcode, which is represented by the fifth row, labeled "/digit (Opcode)". The four rows above give the byte, word and doubleword general-purpose registers and the MMX registers that correspond to the register numbers, with the same assignments as for the R/M field when Mod field encoding is 11B. As with the R/M field register options, which of the four possible registers is used is determined by the opcode byte along with the operand-size attribute.

The body of Tables 2-1 and 2-2 (under the label "Value of ModR/M Byte (in Hexadecimal)") contains a 32 by 8 array giving all of the 256 values of the ModR/M byte, in hexadecimal. Bits 3, 4 and 5 are specified by the column of the table in which a byte resides, and the row specifies bits 0, 1 and 2, and also bits 6 and 7.

Table 2-1. 16-Bit Addressing Forms with the ModR/M Byte

| r8(/r)<br>r16(/r)<br>r32(/r)<br>mm(/r)<br>/digit (Opcode)<br>REG =                                                                  |     |                                                      | AL<br>AX<br>EAX<br>MM0<br>0                  | CL<br>CX<br>ECX<br>MM1<br>1                  | DL<br>DX<br>EDX<br>MM2<br>2<br>010           | BL<br>BX<br>EBX<br>MM3<br>3<br>011           | AH<br>SP<br>ESP<br>MM4<br>4<br>100           | CH<br>BP <sup>1</sup><br>EBP<br>MM5<br>5     | DH<br>SI<br>ESI<br>MM6<br>6<br>110           | BH<br>DI<br>EDI<br>MM7<br>7<br>111           |

|-------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|

| Effective<br>Address                                                                                                                | Mod | R/M                                                  |                                              | Val                                          | ue of Mo                                     | dR/M By                                      | /te (in H                                    | exadecin                                     | nal)                                         |                                              |

| [BX+SI]<br>[BX+DI]<br>[BP+SI]<br>[BP+DI]<br>[SI]<br>[DI]<br>disp16 <sup>2</sup><br>[BX]                                             | 00  | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 00<br>01<br>02<br>03<br>04<br>05<br>06<br>07 | 08<br>09<br>0A<br>0B<br>0C<br>0D<br>0E<br>0F | 10<br>11<br>12<br>13<br>14<br>15<br>16       | 18<br>19<br>1A<br>1B<br>1C<br>1D<br>1E<br>1F | 20<br>21<br>22<br>23<br>24<br>25<br>26<br>27 | 28<br>29<br>2A<br>2B<br>2C<br>2D<br>2E<br>2F | 30<br>31<br>32<br>33<br>34<br>35<br>36<br>37 | 38<br>39<br>3A<br>3B<br>3C<br>3D<br>3E<br>3F |

| [BX+SI]+disp8 <sup>3</sup> [BX+DI]+disp8 [BP+SI]+disp8 [BP+DI]+disp8 [SI]+disp8 [DI]+disp8 [BP]+disp8 [BY]+disp8                    | 01  | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 40<br>41<br>42<br>43<br>44<br>45<br>46<br>47 | 48<br>49<br>4A<br>4B<br>4C<br>4D<br>4E<br>4F | 50<br>51<br>52<br>53<br>54<br>55<br>56<br>57 | 58<br>59<br>5A<br>5B<br>5C<br>5D<br>5E<br>5F | 60<br>61<br>62<br>63<br>64<br>65<br>66<br>67 | 68<br>69<br>6A<br>6B<br>6C<br>6D<br>6E<br>6F | 70<br>71<br>72<br>73<br>74<br>75<br>76<br>77 | 78<br>79<br>7A<br>7B<br>7C<br>7D<br>7E<br>7F |

| [BX+SI]+disp16<br>[BX+DI]+disp16<br>[BP+SI]+disp16<br>[BP+DI]+disp16<br>[SI]+disp16<br>[DI]+disp16<br>[BP]+disp16<br>[BX]+disp16    | 10  | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 80<br>81<br>82<br>83<br>84<br>85<br>86<br>87 | 88<br>89<br>8A<br>8B<br>8C<br>8D<br>8E<br>8F | 90<br>91<br>92<br>93<br>94<br>95<br>96<br>97 | 98<br>99<br>9A<br>9B<br>9C<br>9D<br>9E<br>9F | A0<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7 | A8<br>A9<br>AA<br>AB<br>AC<br>AD<br>AE<br>AF | B0<br>B1<br>B2<br>B3<br>B4<br>B5<br>B6<br>B7 | B8<br>B9<br>BA<br>BB<br>BC<br>BD<br>BE<br>BF |

| EAX/AX/AL/MM0<br>ECX/CX/CL/MM1<br>EDX/DX/DL/MM2<br>EBX/BX/BL/MM3<br>ESP/SP/AHMM4<br>EBP/BP/CH/MM5<br>ESI/SI/DH/MM6<br>EDI/DI/BH/MM7 | 11  | 000<br>001<br>010<br>011<br>100<br>101<br>110        | C0<br>C1<br>C2<br>C3<br>C4<br>C5<br>C6<br>C7 | C8<br>C9<br>CA<br>CB<br>CC<br>CD<br>CE<br>CF | D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7 | D8<br>D9<br>DA<br>DB<br>DC<br>DD<br>DE<br>DF | E0<br>EQ<br>E2<br>E3<br>E4<br>E5<br>E6<br>E7 | E8<br>E9<br>EA<br>EB<br>EC<br>ED<br>EE       | F0<br>F1<br>F2<br>F3<br>F4<br>F5<br>F6<br>F7 | F8<br>F9<br>FA<br>FB<br>FC<br>FD<br>FE<br>FF |

### NOTES:

- The default segment register is SS for the effective addresses containing a BP index, DS for other effective addresses.

- 2. The "disp16" nomenclature denotes a 16-bit displacement following the ModR/M byte, to be added to the index.

- 3. The "disp8" nomenclature denotes an 8-bit displacement following the ModR/M byte, to be sign-extended and added to the index.

Table 2-2. 32-Bit Addressing Forms with the ModR/M Byte

| r8(/r)<br>r16(/r)<br>r32(/r)<br>mm(/r)<br>/digit (Opcode)<br>REG =                                                                   |     |                                                      | AL<br>AX<br>EAX<br>MM0<br>0                  | CL<br>CX<br>ECX<br>MM1<br>1                  | DL<br>DX<br>EDX<br>MM2<br>2<br>010           | BL<br>BX<br>EBX<br>MM3<br>3<br>011           | AH<br>SP<br>ESP<br>MM4<br>4<br>100           | CH<br>BP<br>EBP<br>MM5<br>5<br>101           | DH<br>SI<br>ESI<br>MM6<br>6<br>110           | BH<br>DI<br>EDI<br>MM7<br>7<br>111           |

|--------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|

| Effective<br>Address                                                                                                                 | Mod | R/M                                                  |                                              | Val                                          | ue of Mo                                     | dR/M By                                      | /te (in H                                    | exadecir                                     | nal)                                         |                                              |

| [EAX]<br>[ECX]<br>[EDX]<br>[EBX]<br>[][] <sup>1</sup><br>disp32 <sup>2</sup><br>[ESI]<br>[EDI]                                       | 00  | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 00<br>01<br>02<br>03<br>04<br>05<br>06<br>07 | 08<br>09<br>0A<br>0B<br>0C<br>0D<br>0E<br>0F | 10<br>11<br>12<br>13<br>14<br>15<br>16<br>17 | 18<br>19<br>1A<br>1B<br>1C<br>1D<br>1E<br>1F | 20<br>21<br>22<br>23<br>24<br>25<br>26<br>27 | 28<br>29<br>2A<br>2B<br>2C<br>2D<br>2E<br>2F | 30<br>31<br>32<br>33<br>34<br>35<br>36<br>37 | 38<br>39<br>3A<br>3B<br>3C<br>3D<br>3E<br>3F |

| disp8[EAX] <sup>3</sup> disp8[ECX] disp8[EDX] disp8[EBX]; disp8[][] disp8[EBP] disp8[ESI] disp8[EDI]                                 | 01  | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 40<br>41<br>42<br>43<br>44<br>45<br>46<br>47 | 48<br>49<br>4A<br>4B<br>4C<br>4D<br>4E<br>4F | 50<br>51<br>52<br>53<br>54<br>55<br>56<br>57 | 58<br>59<br>5A<br>5B<br>5C<br>5D<br>5E<br>5F | 60<br>61<br>62<br>63<br>64<br>65<br>66<br>67 | 68<br>69<br>6A<br>6B<br>6C<br>6D<br>6E<br>6F | 70<br>71<br>72<br>73<br>74<br>75<br>76<br>77 | 78<br>79<br>7A<br>7B<br>7C<br>7D<br>7E<br>7F |

| disp32[EAX]<br>disp32[ECX]<br>disp32[EDX]<br>disp32[EBX]<br>disp32[][]<br>disp32[EBP]<br>disp32[ESI]<br>disp32[EDI]                  | 10  | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 80<br>81<br>82<br>83<br>84<br>85<br>86<br>87 | 88<br>89<br>8A<br>8B<br>8C<br>8D<br>8E<br>8F | 90<br>91<br>92<br>93<br>94<br>95<br>96<br>97 | 98<br>99<br>9A<br>9B<br>9C<br>9D<br>9E<br>9F | A0<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7 | A8<br>A9<br>AA<br>AB<br>AC<br>AD<br>AE<br>AF | B0<br>B1<br>B2<br>B3<br>B4<br>B5<br>B6<br>B7 | B8<br>B9<br>BA<br>BB<br>BC<br>BD<br>BE<br>BF |

| EAX/AX/AL/MM0<br>ECX/CX/CL/MM1<br>EDX/DX/DL/MM2<br>EBX/BX/BL/MM3<br>ESP/SP/AH/MM4<br>EBP/BP/CH/MM5<br>ESI/SI/DH/MM6<br>EDI/DI/BH/MM7 | 11  | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | C0<br>C1<br>C2<br>C3<br>C4<br>C5<br>C6<br>C7 | C8<br>C9<br>CA<br>CB<br>CC<br>CD<br>CE<br>CF | D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7 | D8<br>D9<br>DA<br>DB<br>DC<br>DD<br>DE<br>DF | E0<br>E1<br>E2<br>E3<br>E4<br>E5<br>E6<br>E7 | E8<br>E9<br>EA<br>EB<br>EC<br>ED<br>EE       | F0<br>F1<br>F2<br>F3<br>F4<br>F5<br>F6<br>F7 | F8<br>F9<br>FA<br>FB<br>FC<br>FD<br>FE<br>FF |

### NOTES:

- 1. The [--][--] nomenclature means a SIB follows the ModR/M byte.

- 2. The disp32 nomenclature denotes a 32-bit displacement following the SIB byte, to be added to the index.

- 3. The disp8 nomenclature denotes an 8-bit displacement following the SIB byte, to be sign-extended and added to the index.

Table 2-3 is organized similarly to Tables 2-1 and 2-2, except that its body gives the 256 possible values of the SIB byte, in hexadecimal. Which of the 8 general-purpose registers will be used as base is indicated across the top of the table, along with the corresponding values of the base field (bits 0, 1 and 2) in decimal and binary. The rows indicate which register is used as the index (determined by bits 3, 4 and 5) along with the scaling factor (determined by bits 6 and 7).

Table 2-3. 32-Bit Addressing Forms with the SIB Byte

| r32<br>Base =<br>Base =                                                           |    |                                                      | EAX<br>0<br>000                              | ECX<br>1<br>001                              | EDX<br>2<br>010                              | EBX<br>3<br>011                              | ESP<br>4<br>100                              | [*]<br>5<br>101                              | ESI<br>6<br>110                              | EDI<br>7<br>111                              |

|-----------------------------------------------------------------------------------|----|------------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|

| Scaled Index                                                                      | SS | Index                                                | Value of SIB Byte (in Hexadecimal)           |                                              |                                              |                                              | 111                                          |                                              |                                              |                                              |

| [EAX] [ECX] [EDX] [EBX] none [EBP] [ESI] [EDI]                                    | 00 | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 00<br>08<br>10<br>18<br>20<br>28<br>30<br>38 | 01<br>09<br>11<br>19<br>21<br>29<br>31<br>39 | 02<br>0A<br>12<br>1A<br>22<br>2A<br>32<br>3A | 03<br>0B<br>13<br>1B<br>23<br>2B<br>33<br>3B | 04<br>0C<br>14<br>1C<br>24<br>2C<br>34<br>3C | 05<br>0D<br>15<br>1D<br>25<br>2D<br>35<br>3D | 06<br>0E<br>16<br>1E<br>26<br>2E<br>36<br>3E | 07<br>0F<br>17<br>1F<br>27<br>2F<br>37<br>3F |

| [EAX*2]<br>[ECX*2]<br>[EDX*2]<br>[EBX*2]<br>none<br>[EBP*2]<br>[ESI*2]<br>[EDI*2] | 01 | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 40<br>48<br>50<br>58<br>60<br>68<br>70<br>78 | 41<br>49<br>51<br>59<br>61<br>69<br>71<br>79 | 42<br>4A<br>52<br>5A<br>62<br>6A<br>72<br>7A | 43<br>4B<br>53<br>5B<br>63<br>6B<br>73<br>7B | 44<br>4C<br>54<br>5C<br>64<br>6C<br>74<br>7C | 45<br>4D<br>55<br>5D<br>65<br>6D<br>75<br>7D | 46<br>4E<br>56<br>5E<br>66<br>6E<br>76<br>7E | 47<br>4F<br>57<br>5F<br>67<br>6F<br>77       |

| [EAX*4]<br>[ECX*4]<br>[EDX*4]<br>[EBX*4]<br>none<br>[EBP*4]<br>[ESI*4]<br>[EDI*4] | 10 | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 80<br>88<br>90<br>98<br>A0<br>A8<br>B0<br>B8 | 81<br>89<br>91<br>89<br>A1<br>A9<br>B1<br>B9 | 82<br>8A<br>92<br>9A<br>A2<br>AA<br>B2<br>BA | 83<br>8B<br>93<br>9B<br>A3<br>AB<br>B3<br>BB | 84<br>8C<br>94<br>9C<br>A4<br>AC<br>B4<br>BC | 85<br>8D<br>95<br>9D<br>A5<br>AD<br>B5<br>BD | 86<br>8E<br>96<br>9E<br>A6<br>AE<br>B6<br>BE | 87<br>8F<br>97<br>9F<br>A7<br>AF<br>B7       |

| [EAX*8]<br>[ECX*8]<br>[EDX*8]<br>[EBX*8]<br>none<br>[EBP*8]<br>[ESI*8]<br>[EDI*8] | 11 | 000<br>001<br>010<br>011<br>100<br>101<br>110        | C0<br>C8<br>D0<br>D8<br>E0<br>E8<br>F0<br>F8 | C1<br>C9<br>D1<br>D9<br>E1<br>E9<br>F1       | C2<br>CA<br>D2<br>DA<br>E2<br>EA<br>F2<br>FA | C3<br>CB<br>D3<br>DB<br>E3<br>EB<br>F3<br>FB | C4<br>CC<br>D4<br>DC<br>E4<br>EC<br>F4<br>FC | C5<br>CD<br>D5<br>DD<br>E5<br>ED<br>F5<br>FD | C6<br>CE<br>D6<br>DE<br>E6<br>EE<br>F6<br>FE | C7<br>CF<br>D7<br>DF<br>E7<br>EF<br>F7       |

### NOTE:

1. The [\*] nomenclature means a disp32 with no base if MOD is 00, [EBP] otherwise. This provides the following addressing modes:

disp32[index] (MOD=00). disp8[EBP][index] (MOD=01). disp32[EBP][index] (MOD=10).

## **Instruction Set Reference**

## CHAPTER 3 INSTRUCTION SET REFERENCE

This chapter describes the complete Intel Architecture instruction set, including the integer, floating-point, MMX technology, and system instructions. The instruction descriptions are arranged in alphabetical order. For each instruction, the forms are given for each operand combination, including the opcode, operands required, and a description. Also given for each instruction are a description of the instruction and its operands, an operational description, a description of the effect of the instructions on flags in the EFLAGS register, and a summary of the exceptions that can be generated.

### 3.1. INTERPRETING THE INSTRUCTION REFERENCE PAGES

This section describes the information contained in the various sections of the instruction reference pages that make up the majority of this chapter. It also explains the notational conventions and abbreviations used in these sections.

### 3.1.1. Instruction Format

The following is an example of the format used for each Intel Architecture instruction description in this chapter:

### **CMC—Complement Carry Flag**

| Opcode | Instruction | Description           |

|--------|-------------|-----------------------|

| F5     | CMC         | Complement carry flag |

### 3.1.1.1. OPCODE COLUMN

The "Opcode" column gives the complete object code produced for each form of the instruction. When possible, the codes are given as hexadecimal bytes, in the same order in which they appear in memory. Definitions of entries other than hexadecimal bytes are as follows:

- /digit—A digit between 0 and 7 indicates that the ModR/M byte of the instruction uses only the r/m (register or memory) operand. The reg field contains the digit that provides an extension to the instruction's opcode.

- /r—Indicates that the ModR/M byte of the instruction contains both a register operand and an r/m operand.

#### INSTRUCTION SET REFERENCE

- **cb, cw, cd, cp**—A 1-byte (cb), 2-byte (cw), 4-byte (cd), or 6-byte (cp) value following the opcode that is used to specify a code offset and possibly a new value for the code segment register.

- **ib, iw, id**—A 1-byte (ib), 2-byte (iw), or 4-byte (id) immediate operand to the instruction that follows the opcode, ModR/M bytes or scale-indexing bytes. The opcode determines if the operand is a signed value. All words and doublewords are given with the low-order byte first.

- +rb, +rw, +rd—A register code, from 0 through 7, added to the hexadecimal byte given at the left of the plus sign to form a single opcode byte. The register codes are given in Table 3-1.